기초 문법부터 FPGA 구현 실습까지

폭넓게 배우는 Verilog HDL 설계 실습

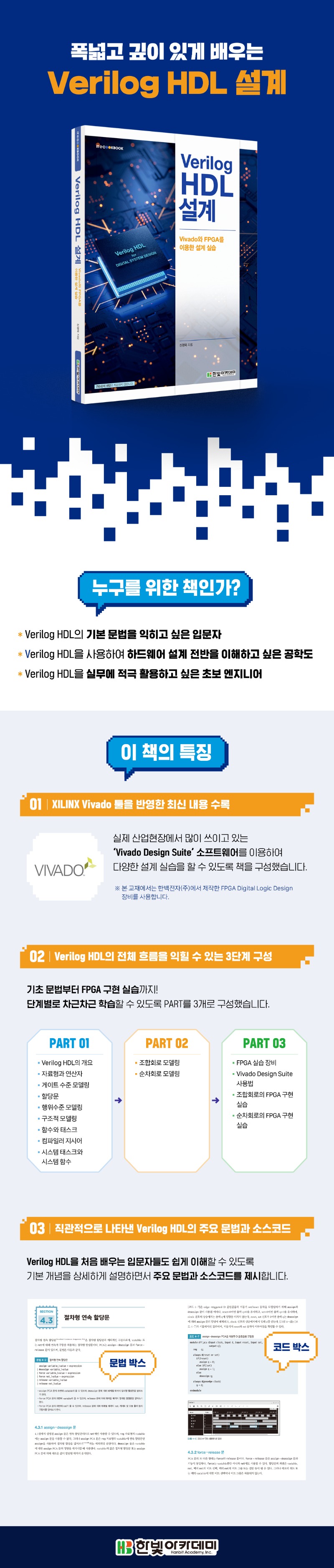

이 책은 디지털 시스템 설계를 배우는 학부생 및 산업체 엔지니어를 대상으로 한다. 총 130여 개의 예시로 Verilog HDL 문법을 체계적으로 소개하며, 입문자도 쉽게 이해할 수 있도록 개념을 간결하고 명확하게 서술한다. 또한, 설계 실습을 통해 Verilog HDL로 설계된 조합회로와 순차회로를 FPGA에 구현하여 하드웨어 동작을 직접 확인할 수 있도록 구성했다.

* 본 도서는 대학 강의용 교재로 개발되었으므로 연습문제 해답은 제공하지 않습니다.

PART 01 Verilog HDL 문법

CHAPTER 01 Verilog HDL의 개요

1.1 Verilog HDL의 역사

1.2 Verilog HDL의 특징

1.3 HDL 기반의 시스템 반도체 설계과정

1.4 Verilog HDL의 어휘 토큰과 규칙

1.5 Verilog HDL 모델링 방법 개요

CHAPTER 02 자료형과 연산자

2.1 Verilog 자료형

2.2 Verilog 연산자

연습문제

CHAPTER 03 게이트 수준 모델링

3.1 기본 논리 게이트 프리미티브

3.2 buf 게이트와 not 게이트 프리미티브

3.3 3상태 버퍼 게이트 프리미티브

3.4 게이트 프리미티브 인스턴스의 배열

3.5 게이트 지연과 net 지연

연습문제

CHAPTER 04 할당문

4.1 연속 할당문

4.2 절차형 할당문

4.3 절차형 연속 할당문

연습문제

CHAPTER 05 행위수준 모델링

5.1 always 구문과 initial 구문

5.2 절차형 할당문

5.3 if 조건문

5.4 case 문

5.5 반복문

5.6 절차형 할당의 타이밍 제어

5.7 블록문

연습문제

CHAPTER 06 구조적 모델링

6.1 모듈

6.2 모듈 인스턴스

6.3 모듈 parameter

6.4 생성문

6.5 계층적 이름

연습문제

CHAPTER 07 함수와 태스크

7.1 함수와 태스크의 차이점

7.2 함수

7.3 태스크

연습문제

CHAPTER 08 컴파일러 지시어

8.1 문자 매크로 정의 및 해제 지시어

8.2 시간 단위와 정밀도 지정 지시어

8.3 파일 삽입 지시어

8.4 선택적 컴파일 지시어

연습문제

CHAPTER 09 시스템 태스크와 시스템 함수

9.1 디스플레이 시스템 태스크

9.2 파일 처리용 시스템 태스크

9.3 시뮬레이션 제어 시스템 태스크

9.4 변환 시스템 함수

PART 02 Verilog HDL을 이용한 하드웨어 모델링

CHAPTER 10 조합회로 모델링

10.1 기본 논리 게이트 및 단순 조합회로

10.2 멀티플렉서

10.3 인코더와 디코더

10.4 비교기

10.5 3상태 버스

10.6 case 문과 if 문의 합성

CHAPTER 11 순차회로 모델링

11.1 래치와 플립플롭

11.2 순차회로에서 blocking 할당문과 nonblocking 할당문

11.3 계수기와 시프트 레지스터 차

11.4 유한상태머신 회로

PART 03 FPGA 구현 실습

CHAPTER 12 FPGA 실습장비

12.1 FPGA 실습장비 개요

12.2 FPGA 실습장비의 구성

CHAPTER 13 Vivado Design Suite 사용법

13.1 Xilinx Vivado 소프트웨어 개요

13.2 Vivado Project 생성

13.3 설계 입력

13.4 Behavioral 시뮬레이션

13.5 RTL 분석 및 설계 합성

13.6 설계 구현

13.7 Bitstream 생성 및 디바이스 프로그래밍

CHAPTER 14 조합회로의 FPGA 구현 실습

14.1 기본 논리 게이트 설계

14.2 가산기와 감산기 회로 설계

14.3 멀티플렉서 설계

14.4 인코더와 디코더 설계

CHAPTER 15 순차회로의 FPGA 구현 실습

15.1 플립플롭과 시프트 레지스터 설계

15.2 계수기 설계

15.3 주파수 분주기 설계

15.4 키패드 스캔 회로 설계

15.5 Piezo 응용회로 설계

15.6 스텝 모터 구동회로 설계

15.7 Color LED 디스플레이 회로 설계

15.8 Text LCD 문자 디스플레이 회로 설계

PART 01 Verilog HDL 문법

Verilog HDL의 어휘 규칙을 비롯해 자료형과 연산자, 할당문, 함수와 태스크 등 디지털 회로 설계 및 합성에 사용되는 Verilog HDL의 기초 문법을 중점적으로 다룬다.

PART 02 Verilog HDL을 이용한 하드웨어 모델링

PART 01에서 설명한 Verilog HDL의 문법을 적용한 하드웨어 설계 방법과 시뮬레이션을 통한 기능 검증 실습을 다룬다.

PART 03 FPGA 구현 실습

설계된 회로를 FPGA 디바이스에 구현하고 하드웨어 동작을 검증하는 과정, FPGA 실습장비와 Vivado Design Suite 툴 사용법, 그리고 다양한 실습 예제들을 포함하고 있다. 이 책의 10장, 11장, 14장, 15장에서는 다양한 설계 실습 예제와 설계과제들을 수록하여 Verilog HDL을 이용한 하드웨어 설계 및 검증 능력을 배양할 수 있도록 했다. 학생들 스스로 설계과제들을 실습해본다면 Verilog HDL에 대한 이해와 응용력뿐만 아니라 실무 능력도 크게 향상될 것이다.